# Annale OS 2019

Proposition non contractuelle

## Questions de cours

> 1) En mode protégé, pourquoi le registre EIP n'est pas suffisant pour calculer correctement l'adresse de l'instruction courante ?

EIP ne donne que l'offset, il nous manque donc la base du segment pour avoir l'adresse de l'instruction courante.

> 2) Quel est le niveau de privilèges le plus élevé, autorisé par la segmentation ?

PL0 (les niveaux vont de 0 à 3, 3=userland et 0= kernel)

> 3) Par quel procédé peut-on augmenter son niveau de privilèges en mode protégé ?

ljmp pour changer le CS et donc le CPL.

> 4) Par quel procédé peut-on abaisser son niveau de privilèges en mode protégé ?

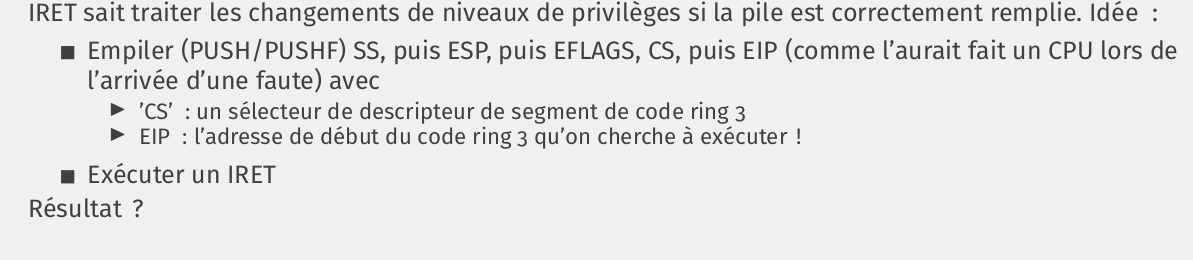

Aves des "Call Gate" ou des "Interrupt Gate"

T'es sûre ? J'aurais dit un iret comme on a fait au TP mais j'avais mal compris

ça

> 5) A quoi sert le TSS dans les OS modernes (Windows/Linux) ?

Gère les interruptions matérielles spécifiques et permet de configurer une tache I/O (i guess)

définir l'emplacement de la pile du noyau lorsqu'une interruption matérielle survien

Alors perso j'avais cru comprendre que c'était une sorte de stockage de tous les registres utiles (e[abcd]x, e[sb]p, [cds]r ...) lors de l'arrivée d'une interruption pour le restaurer après.

Perso j'avais compris que le TSS sert à sauvegarder le contexte lors d'un passage ring 3 $\Rightarrow$ ring 0 et inversement.

> 6) A quelle(s) faille(s) de sécurité élémentaire l’implémentation des appels systèmes peut- elle être exposée ?

pas au programme

J'aurais dit élévation de privilège.

> 7) Citez un intérêt, du point de vue de la sécurité, offert par la pagination.

protège le noyau des tâches

J'aurais dit que ça permet de mettre en place une segmentation de la mémoire et du coup on protège une tache d'une autre et le noyau des tâches

Perso j'aurais dit que ça permet de mieux gérer les niveaux de privilèges et une meilleure gestion de la mémoire.

> 8) Quel problème de sécurité majeur pose le bit R/W des entrées de tables de pages ?

idk

> 9) Combien de niveaux de privilèges existe-t-il lorsque l’on utilise la pagination ?

4 -> 0,1,2,3

Je dirais 2 tu as user et supervisor. C'est la segmentation qui donne les 4 rings non ?

Ça faut que 1 bit sur leur schéma donc que 2 à mon sens

> 10) Que se passe-t-il lorsqu’on accède au registre CR0 en ring 3 ?

General protection Fault -> on accède à un registre auquel on a pas le droit avec le CPL.

> 11) Expliquez pourquoi il est dangereux, pour un noyau, de sauver le contexte d’une tâche dans la mémoire utilisateur de cette tâche. Dans quelle zone de mémoire un noyau devrait-t-il le sauvegarder ?

Cela peut exposer des informations sensibles qui vont donner lieu à des fuites. On s'expose également à des modifications de la part de l'utilisateur ce qui donnera des comportements non-prévus.

> 12) Quels sont les avantages, toujours du point de vue de la sécurité, des micro-noyaux par rapport aux noyaux monolithiques ?

isolations des composants, réduction de la surface d'attaque, séparation des privilèges.

## Problème 1 : Pagination

Dans la suite de l’énoncé, PPN signifie Physical Page Number (numéro de page physique). Considérons la configuration suivante de tables de pages pour un processeur Intel x86 32 bits.

Le Page Directory à l’adresse physique 0x00001000 contient:

-PDE 0: PPN=0x00002, PTE_P, PTE_U, PTE_W

PDE 1: PPN=0x00003, PTE_P, PTE_U, PTE_W

PDE 2: PPN=0x00002, PTE_P, PTE_U, PTE_W ...

les autres PDEs sont à zéro

-La Page Table 1 à l’adresse physique 0x00002000 (PPN 0x00002) contient:

PTE 0: PPN=0x00005, PTE_P, PTE_U, PTE_W

PTE 1: PPN=0x00006, PTE_P, PTE_U, PTE_W ...

les autres PTEs sont à zéro

-La Page Table 2 à l’adresse physique 0x00003000 contient:

PTE 0: PPN=0x00005, PTE_P, PTE_U, PTE_W

PTE 1: PPN=0x00005, PTE_P, PTE_U, PTE_W ...

les autres PTEs sont à zéro

### Questions :

Disclamer : les réponses ci dessous n'engagent que moi lol

> 1 - Listez toutes les adresses virtuelles qui mappent l’adresse physique 0x00005555.

Sincérement sans calculette ou convertisseur c'est impossible ou alors on est des crack (ou alors j'ai rien comrpis à la traduction d'adresses)

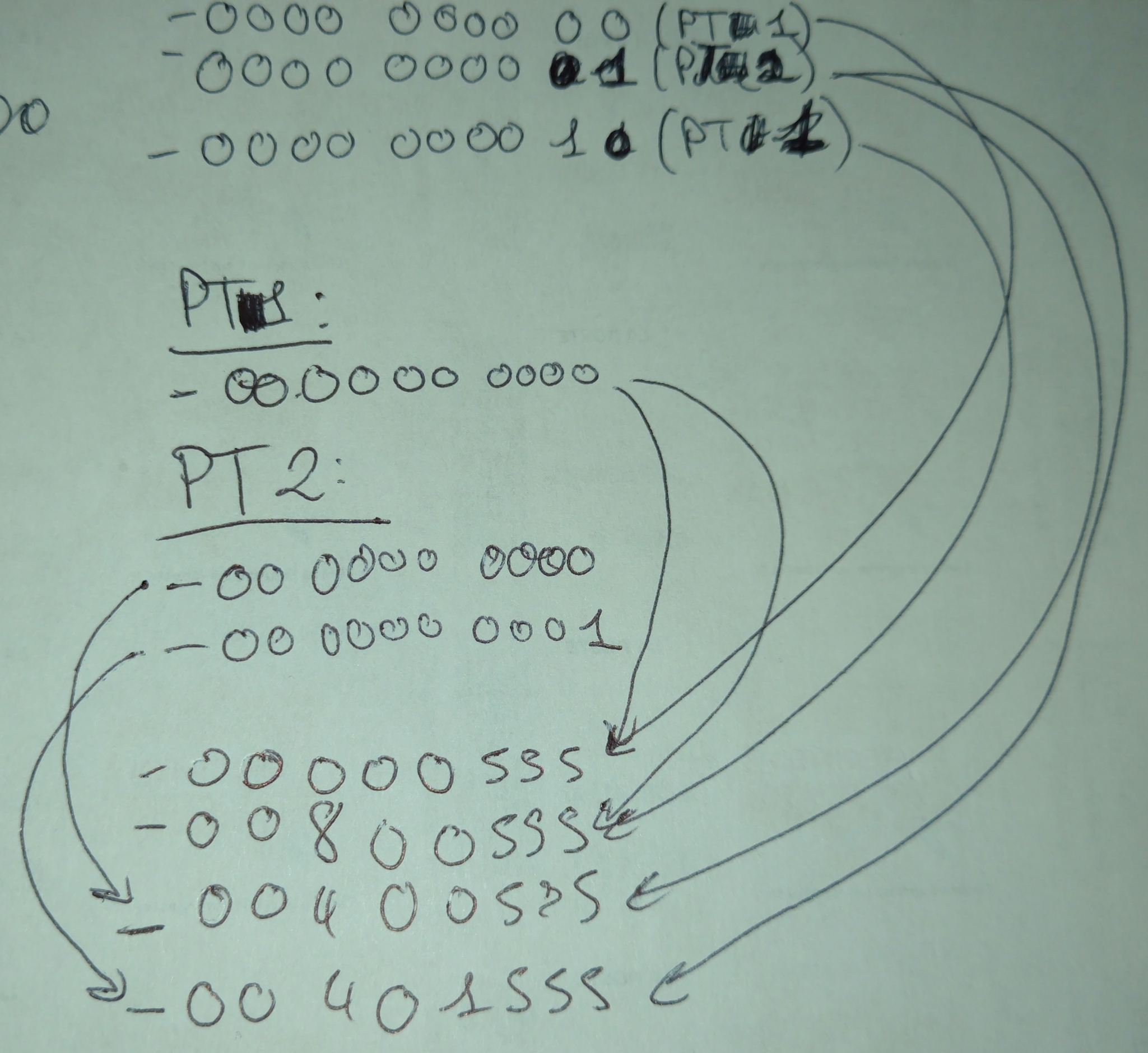

Perso j'aurais dit que chaque PPN représente $2^{12}$ adresses et donc en sachant ça la PPN 0 représentée par 0x00000 contient les adresses physiques de 0 à 4095 (0x0000 à 0x0fff), la PPN 1 représentée par 0x00001 contient les adresses physiques 4096 à 8191 (0x1000 à 0x1fff). Donc l'adresse que l'on veut est contenu dans la PPN 5 (qui contient les adresses de 0x5000 à 0x5fff) et plus qu'à regarder combien d'adresse virtuelle map cette page. Donc je dirais : `0x00000555`, `0x00400555`, `0x00401555` et `0x00800555`

J'ai exactement pareil voila comment j'ai énuméré les différentes adresses possibles :

> 2 - L’adresse virtuelle 0x402000 ${(4*1024*1024 + 8192)}$ est-elle mappée ?

Non, offset de 4 dans la PGD or pas de PDE à l'index 4.

Perso j'aurais dit : 0x402000 -> 0x00402000 -> 0000 0000 0100 0000 0010 0000 0000 0000 -> 0000 0000 01 (=1 idx PGD) 00 0000 0010 (=2 idx PTB) 0000 0000 0000 (=0 idx PPN). Donc non elle n'est pas mappé car dans l'index 1 de la PDG il y a la PTB2 et que cette PTB n'a pas l'entrée d'index 2.

> 3 - A quelle adresse virtuelle (s’il en est) le noyau doit-il écrire pour modifier le mapping de l’adresse virtuelle 0x402000 ?

Pas possible car le PGD qui est à 0x1000 n'est pas mappé si j'ai bien capté.

Ouais je dirais pareil mais 0 promesse ^^'

> 4 - Expliquez précisément ce que la Page Table 2 devrait contenir afin de permettre au noyau d’écrire dans le Page Directory. Plusieurs réponses sont possibles. Expliquez-en une.

Beh du coup on donnne une PTE en mode

```

PTE 2 : PPN = 0x00001, ...

```

dans la PGT 2. Et dans ce cas là par exemple une addresse en 0x00402XXX tapperait en 0x00001XXX soit à l'addresse du XXXe PDE (je croé)

## Problème 2 :

Imaginez un noyau de système d’exploitation offrant de la sécurité (isolation des tâches et du noyau) sans le mécanisme matériel des appels systèmes (int XX, sysenter/sysexit).

### Questions :

> 1 - Citez les éléments du processeur que le noyau doit configurer pour mettre en place une isolation ring 3 / ring 0.

La segmentation peut être la pagination aussi

la segmentation avec la GDT, les Selecteur/descripteur qui auront à chaque fois les privilège levels. le CPL dans CR3.

> 2 - Proposez une solution permettant au ring 3 de communiquer avec le ring 0 sans compromettre la sécurité du système.

Les syscalls ? c'est cool les syscalls non ?

> 3 - Quelles sont les vulnérabilités potentielles de votre solution ? Comment les éviter ?

heu ... les syscalls c'est dangereux (cf Anaïs) ?

> 4 - Décrivez brièvement, l’exécution d’un appel système hypothétique fondé sur votre concept.

ah heu ... ben c'est un syscall